译自原文

Practical N-Type Doping in AlN for Power Electronics

原文作者

C. E. Quiñones1 , P. Bagheri1 , D. Khachariya2 , S. Rathkanthiwar1 , R. Kirste2 , P. Reddy2 , S. Mita2 , E. Kohn1 , R. Collazo1 , Z. Sitar1,2

1Deptartment of Materials Science and Engineering, North Carolina State University,

2Adroit Materials, Inc.

原文链接

https://csmantech.org/paper/practical-n-type-doping-in-aln-for-power-electronics/

全文下载链接

https://csmantech.org/wp-content/uploads/2025/05/2A.1-Final.2025.pdf

摘要

本研究通过在硅掺杂氮化铝(Si:AlN)中引入点缺陷和扩展缺陷调控机制,有效抑制了载流子补偿效应,成功实现了300 cm²/(V·s)的高电子迁移率和26 Ω·cm的低电阻率。基于此掺杂技术,我们设计并制备了高性能氮化铝肖特基势垒二极管。实验结果表明,该器件在正向偏置条件下可实现kA/cm²量级的大电流导通能力,同时具备kV量级的电压阻断特性。这些突破性成果证实了氮化铝材料在下一代功率电子器件领域的应用潜力。

引言

氮化铝(AlN)凭借其超宽带隙、高击穿电场强度、优异的热导率以及出色的高温稳定性,成为极端工况下千伏级功率电子器件的理想候选材料。然而,尽管AlN具备这些卓越特性,其电子器件技术仍处于发展初期阶段,主要技术瓶颈在于掺杂工艺的复杂性——现有掺杂剂的激活能过高,同时补偿缺陷的形成能过低,这使得制备实用化器件面临巨大挑战。近年来,AlN材料研究取得的重要突破性进展为开发基于该材料的高性能器件奠定了坚实基础。研究主要从两个方向展开:其一,在III族氮化物体系中建立了系统的点缺陷调控框架,有效抑制了材料自补偿效应;其二,探索了新型掺杂方法,如组分渐变AlGaN薄膜中的分布极化掺杂技术。本研究创新性地采用化学势调控(CPC)结合缺陷准费米能级(dQFL)控制技术,在生长过程中实现了对Si掺杂AlN缺陷掺入的精确调控。该技术路线成功抑制了主要补偿缺陷,获得了迁移率高达300 cm²/(V·s)的导电AlN薄膜。在此基础上,我们进一步开发了具有国际先进水平的AlN电子器件。通过设计组分渐变结构优化电子输运特性,最终研制出正向电流密度达kA/cm²量级、阻断电压达kV量级的AlN肖特基势垒二极管。

实验方法

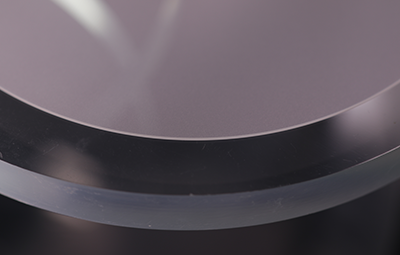

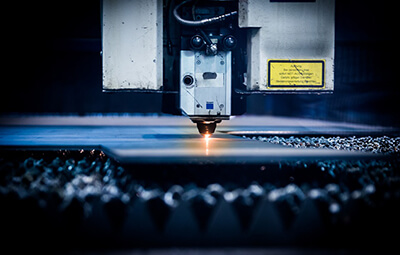

本研究采用射频加热冷壁金属有机化学气相沉积系统(RF-MOCVD),分别以c面蓝宝石衬底和AlN单晶衬底为生长基底,制备n型硅掺杂AlN薄膜。选用三甲基铝(TMA)、氨气(NH₃)和硅烷(SiH₄)分别作为铝源、氮源与硅源。所制备样品采用双层结构:底层为500 nm厚的非故意掺杂(UID)AlN缓冲层,其上外延生长500 nm厚的硅掺杂AlN功能层。通过精确调控硅烷流量,实现n型掺杂层中5×10¹⁷至5×10¹⁹ cm⁻³的硅掺杂浓度。关于衬底预处理及外延生长的具体工艺参数,详见文献[5,7,8,9]。为系统探究化学势调控(CPC)对补偿缺陷的抑制机制,本研究在1100~1400℃温度区间及1000~6000的V/III比范围内(通过调节NH₃流量从0.3至3 slm实现)进行对比生长实验。在材料外延生长过程中采用高于带隙能量的汞灯光源进行原位光辐照处理,以抑制准费米能级(dQFL)点缺陷的形成,该光源具有1 W/cm²的光功率密度以激发少数载流子。电学性能表征方面,采用电子束蒸发工艺制备大面积Cr/Ti/Al/Ti/Au复合电极(各层厚度依次为20/20/100/45/55 nm)。通过Lake Shore 8400系列交流/直流霍尔测量系统,完成样品的霍尔效应及电阻率测试。

AlN肖特基势垒二极管(SBD)结构同样也在AlN单晶衬底上生长完成。器件结构设计如下:在2 μm厚的高掺杂Al₀.₇₅Ga₀.₂₅N接触层(硅掺杂浓度[Si]=1×10¹⁹ cm⁻³)上,外延生长1 μm厚的n型AlN漂移层(硅掺杂浓度[Si]=1×10¹⁸ cm⁻³)。为提升AlN与AlGaN界面处的电子输运效率,特别设计了组分渐变过渡层。器件制备流程采用标准光刻工艺结合反应离子刻蚀技术完成。欧姆接触电极通过电子束蒸发工艺,在刻蚀后的表面沉积Cr/Ti/Al/Ti/Au金属复合层(各层厚度依次为20 nm/20 nm/100 nm/45 nm/55 nm)形成;肖特基接触则采用高纯度镍(Ni)材料,通过电子束蒸发工艺制备圆形电极实现。电学特性测试方面,电流-电压(I-V)特性曲线由Keithley 4200半导体参数分析仪(SCS)精确测量;器件击穿特性在高真空环境中进行表征。

结果与讨论

研究证实,在低掺杂浓度条件下,碳(![]() )复合体与位错构成氮化镓(GaN)中两大主要补偿缺陷类型。具体而言,碳杂质是引发低掺杂浓度区迁移率急剧下降的关键因素;而位错作为受主型补偿中心,其等效受主浓度与位错密度呈显著正相关性。基于此发现,采用低位错密度(<10³ cm⁻²)的AlN单晶衬底可有效抑制位错补偿效应。图1系统呈现了不同生长工艺及衬底类型条件下,室温载流子浓度随硅掺杂浓度的变化规律。通过对比相同生长条件下蓝宝石衬底(黑色圆圈标记)与AlN单晶衬底(红色方块标记)样品的电学性能差异,可清晰揭示位错对掺杂特性的调控作用。实验数据显示:当采用AlN单晶衬底时,器件最大载流子浓度与迁移率均实现双倍提升;同时,有效掺杂窗口可扩展至中低10¹⁸ cm⁻³浓度区间。该现象有力证实,在蓝宝石衬底上生长的薄膜材料在低掺杂区间存在显著的位错补偿效应限制机制。

)复合体与位错构成氮化镓(GaN)中两大主要补偿缺陷类型。具体而言,碳杂质是引发低掺杂浓度区迁移率急剧下降的关键因素;而位错作为受主型补偿中心,其等效受主浓度与位错密度呈显著正相关性。基于此发现,采用低位错密度(<10³ cm⁻²)的AlN单晶衬底可有效抑制位错补偿效应。图1系统呈现了不同生长工艺及衬底类型条件下,室温载流子浓度随硅掺杂浓度的变化规律。通过对比相同生长条件下蓝宝石衬底(黑色圆圈标记)与AlN单晶衬底(红色方块标记)样品的电学性能差异,可清晰揭示位错对掺杂特性的调控作用。实验数据显示:当采用AlN单晶衬底时,器件最大载流子浓度与迁移率均实现双倍提升;同时,有效掺杂窗口可扩展至中低10¹⁸ cm⁻³浓度区间。该现象有力证实,在蓝宝石衬底上生长的薄膜材料在低掺杂区间存在显著的位错补偿效应限制机制。

图1 不同生长条件与衬底下,室温载流子浓度(a)及霍尔迁移率(b)随硅掺杂浓度的变化关系

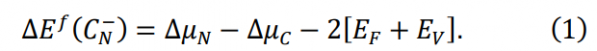

为有效抑制C-N复合体(![]() )的形成,需采用点缺陷调控技术。碳原子在晶体生长过程中的掺杂行为由缺陷形成能决定,该能量与氮(μₙ)、碳(μc)的化学势及费米能级相对价带顶的位置(EF - EV)密切相关。

)的形成,需采用点缺陷调控技术。碳原子在晶体生长过程中的掺杂行为由缺陷形成能决定,该能量与氮(μₙ)、碳(μc)的化学势及费米能级相对价带顶的位置(EF - EV)密切相关。

本研究提出的点缺陷调控方案正是基于上述物理机制。为实现碳掺杂浓度的精确调控,可通过生长参数优化调控两个核心变量:氮化学势与费米能级。具体实施路径如下:通过提高氨气流量以增大V/III比(即N/Al化学计量比),可在生长体系中构建富N环境,从而增大N化学势差Δμₙ,显著抑制![]() 复合体的形成。实验数据显示(图1):当V/III比由1000提升至6000时,器件最大迁移率从80 cm²/(V·s)显著提升至300 cm²/(V·s),同时低掺杂浓度下限从[Si]=1×10¹⁷ cm⁻³扩展至1×10¹⁸ cm⁻³;进一步引入波长大于带隙的紫外光照射,可将掺杂浓度下限进一步降低至<10¹⁸ cm⁻³,同时维持300 cm²/(V·s)的高迁移率特性。上述实验结果证实,通过系统实施点缺陷调控技术,可有效抑制

复合体的形成。实验数据显示(图1):当V/III比由1000提升至6000时,器件最大迁移率从80 cm²/(V·s)显著提升至300 cm²/(V·s),同时低掺杂浓度下限从[Si]=1×10¹⁷ cm⁻³扩展至1×10¹⁸ cm⁻³;进一步引入波长大于带隙的紫外光照射,可将掺杂浓度下限进一步降低至<10¹⁸ cm⁻³,同时维持300 cm²/(V·s)的高迁移率特性。上述实验结果证实,通过系统实施点缺陷调控技术,可有效抑制![]() (C-N复合体)的形成。

(C-N复合体)的形成。

为建立补偿效应与生长条件间的定量关系,我们对掺杂AlN薄膜开展了系统的变温霍尔测试。图2(a)呈现了具有代表性的载流子浓度-温度依赖曲线。通过将实验测得的温度依赖性载流子浓度数据与电荷平衡模型进行拟合,成功提取了关键参数:掺杂离子激活能(Δ𝜖𝑆𝑖)和补偿受主浓度(NA)。与此同时,基于马西森定则(Matthiessen’s rule)并综合考虑典型散射机制,构建了迁移率随温度变化的数学模型,该模型实现了从温度依赖的迁移率数据中提取电离杂质浓度。图2(b)整合了载流子浓度和迁移率的双重拟合结果,系统揭示了电离受主浓度随生长参数调控及衬底类型变化的演变规律。实验数据显示:通过同步实施点缺陷调控与扩展缺陷抑制的协同策略,补偿缺陷浓度实现了近两个数量级的显著降低。这一定量分析结果有力证实,在超宽禁带AlN材料体系中,采用系统化的点缺陷调控技术并优化衬底选择,可实现对补偿效应的有效抑制。

图2(a) 在V/III比为3000、生长温度1100℃条件下制备的硅掺杂AlN薄膜(硅掺杂浓度[Si]=3×10¹⁸ cm⁻³)的载流子浓度随温度变化曲线;(b) 基于电荷平衡模型与迁移率拟合提取的电离受主浓度随生长条件及衬底类型的变化关系

基于已掌握的AlN有效掺杂技术,我们成功设计并制备了AlN肖特基势垒二极管。图3(a)展示了器件的典型电流-电压(I-V)特性曲线,插图为器件横截面的结构示意图。该器件采用多层复合结构设计:n型AlN漂移层作为主电流通道,n⁺-AlGaN接触层用于优化欧姆接触,中间引入100 nm厚的铝组分渐变过渡层——其铝组分从接触层端的富Al状态至漂移层端的富N状态呈线性梯度分布。漂移层掺杂浓度经优化设计,实现了电导率的最大化。前期霍尔测试结果表明,器件关键参数达到预期目标:载流子浓度2×10¹⁵ cm⁻³、迁移率160 cm²/(V·s)、电阻率26 Ω·cm。如图3(b)所示,器件展现出1.1的超低理想因子,证实其载流子输运过程接近理想热电子发射机制。在正向偏置条件下,器件实现了>3 kA/cm²的超高电流密度,较现有文献报道[11]-[23]实现了数量级的性能突破。器件的整流特性优异,开关比高达10¹³量级。特别值得注意的是,微分比导通电阻(RON)低至<1 mΩ·cm²,创造了AlN基功率器件的新纪录。

图3展示了所制备的AlN肖特基势垒二极管的电流-电压(I-V)特性曲线,其中左图采用半对数坐标(纵轴对数刻度),右图采用线性坐标。插图为最终制备完成的器件结构剖面示意图。

图4(a)呈现了所制备器件的反向偏置电流-电压(I-V)特性曲线。通过曲线拟合测得其击穿电压VBD为680 V,该击穿电压定义为器件在反向偏置状态下电流密度达到10⁻³ A/cm²时对应的电压值。为验证实验结果的可靠性,我们基于Silvaco TCAD仿真平台构建了相同器件结构的数值模型,模拟结果显示其理论击穿电压VBD为717V。值得注意的是,仿真结果与实验测量值(680 V)的相对误差仅为5.2%,表现出高度的一致性,这为器件物理机制的分析提供了可靠依据。进一步地,为深入探究AlN漂移层中的电场分布特性,图4(b)展示了器件在680 V反向偏置条件下的仿真电场强度分布曲线。分析表明,在实验击穿电压工况下,器件内部最大电场强度达到12.3 MV/cm。这一数值结果直接反映了材料本身的耐压特性,为后续器件优化设计提供了关键参数支撑。特别需要指出的是,本研究中的器件结构采用全横向设计,未引入任何诸如场板、阶梯结等人为设计的电场调控结构。这一设计特点使得实验结果能够真实反映材料本征的耐压特性,为AlN材料在高压功率器件领域的应用提供了基础数据支撑。

图4(a)展示了所制备AlN肖特基势垒二极管的反向偏置电流-电压(I-V)特性曲线,测得其击穿电压为V=-680 V。图4(b)呈现了器件在实验击穿电压条件下的仿真电场分布曲线,结果显示漂移层内最大电场强度达到12.3 MV/cm。

结论

本研究证实,通过实施点缺陷调控方法,可在AlN中实现有效的n型掺杂。具体而言,通过优化衬底选择、化学势及缺陷准费米能级调控,成功将AlN的低掺杂极限拓展至中等数量级10¹⁷ cm⁻³的硅(Si)掺杂浓度。基于此基础研究成果,我们进一步设计并制备了具有实用价值的AlN肖特基势垒二极管。所研制的器件展现出国际领先水平的关键性能指标:高电流密度(>3 kA/cm²)、低微分导通电阻(<1 mΩ·cm²)及高击穿电压(680 V)。这些成果充分证明,在生长过程中精准调控杂质与缺陷的掺入行为,是开发新一代超宽禁带半导体(如AlN)高性能器件的核心关键。

原文源于【CS MANTECH】官网

(以上文章由奥趋光电翻译,如有涉及版权等问题,请联系我们以便处理)